Louisiana Tech University

Email: mahmed@latech.edu

The funded PhD positions have been filled. LATECH thesis and senior capstone students are strongly encouraged to reach out and engage in for-credit research opportunities in Machine Learning, Computer Architecture, FPGA design, and Electronic Design Automation. We dont offer and decide for TA positions.

We Are Hiring: Fully Funded PhD Positions Available (Spring 2026)

We are currently seeking highly motivated Ph.D. and Master’s students to join our research at Louisiana Tech University starting Spring 2026. Fully funded positions are available for students interested in cutting-edge research at the intersection of electronic design automation and machine learning. Our current projects focus on emerging and future computing architectures, energy-efficient and domain-specific computing, and the integration and validation of heterogeneous systems.

Candidates should have a strong background in computer architecture, digital system design, and computing systems, with proficiency in C++ or Python; particularly in graph algorithms. A bachelor’s degree in computer science, computer engineering, electrical engineering, or a closely related field is required.

To apply, please email your resume, transcripts, GRE/TOEFL scores, and any relevant publications, writing samples highlighting relevant skills to rubelahmed@ieee.org. Additional supporting documents are welcome. For more information about the graduate program, visit https://coes.latech.edu/graduate-programs/ .

Louisiana Tech University is located in Ruston, a welcoming and safe college town in northern Louisiana. Ruston offers a close-knit community, affordable living, and a vibrant student-friendly environment. The city is about an hour from Shreveport and roughly three and half hours from Dallas, Texas, providing access to major city amenities while maintaining a relaxed, small-town charm.

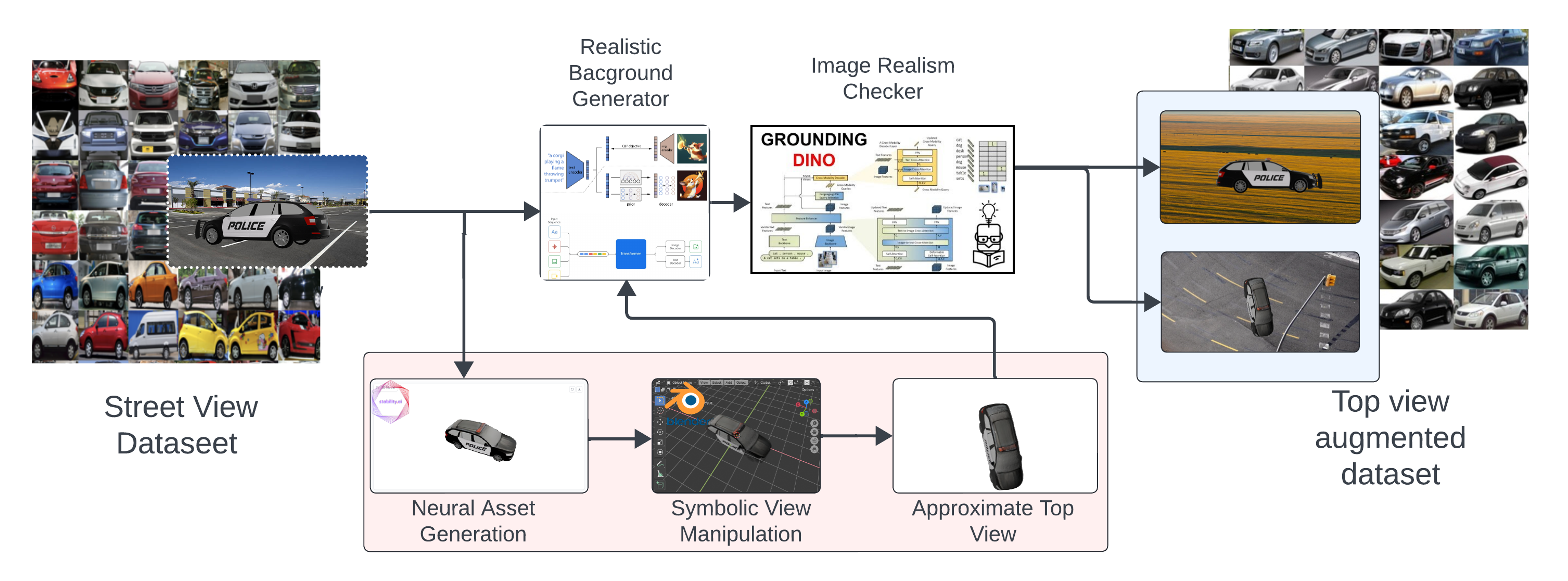

Trustworthy Autonomous Systems via Neuro-Symbolic Learning

The Assured Neuro-Symbolic Learning and Reasoning (ANSR) program aims to overcome the critical barriers

that have hindered the realization of AI in safety and mission-critical autonomous systems. DARPA

addresses two reasons for this. ''First, data-driven ML lacks transparency, interpretability, and

robustness and has unsustainable computational and data needs. Second, traditional approaches to

building

intelligent applications and autonomous systems that rely on knowledge representations and symbolic

reasoning

can be assured but are not robust to the uncertainties encountered in the real world.''

Our research directly addresses these challenges by pioneering a novel neuro-symbolic AI framework that

enhances 3D scene representation in autonomous drones, aligning with the core objectives of the ANSR

initiative.

Our research enhances 3D scene representation and reasoning in autonomous drones by leveraging

neuro-symbolic AI.

Traditional methods for 3D scene representation relying on dense point clouds are data-inefficient and

lack

interpretability. We address this by integrating symbolic object models using the Universal Scene

Description (USD) language. Our Neuro-Symbolic Conversion (NSC) framework automates object

identification

within point clouds, substitutes them with symbolic models, and validates these substitutions through

visual

comparison, improving data efficiency and reasoning for downstream scenarios understanding tasks

efficiency.

The attached images illustrate our innovative approach, where object-wise point-cloud generation and

symbolic

representation in USD files create more interpretable and efficient 3D models. By matching objects using

metrics such as Mean Squared Error (MSE) and Structural Similarity Index (SSIM), we ensure the accuracy

and

robustness of these symbolic models. This methodology significantly contributes to the development of

trustworthy autonomous systems, aligning with the objectives of the ANSR program. Our research has been

recognized and published in prestigious AI venues, including the AAAI Workshop and ICAA, underscoring

its

impact in the field.

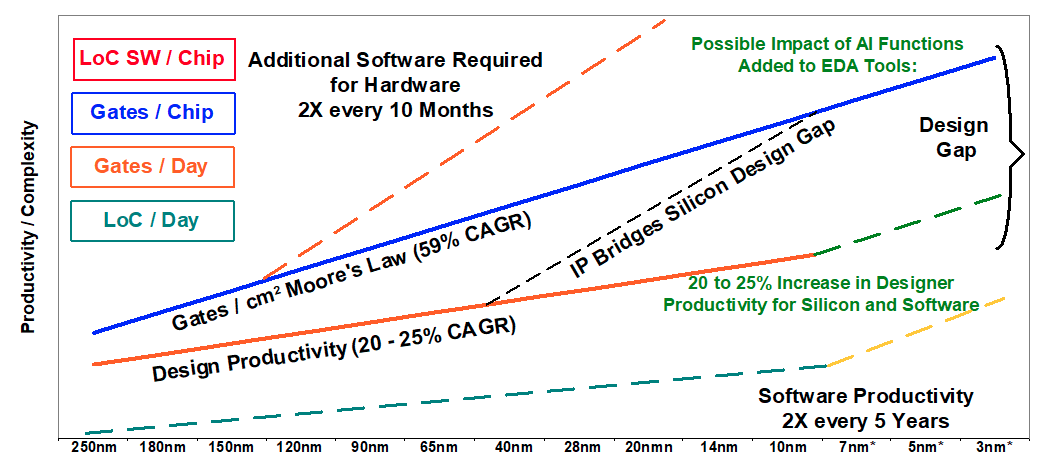

Machine Learning for Electronic Design Automation

Specification Mining

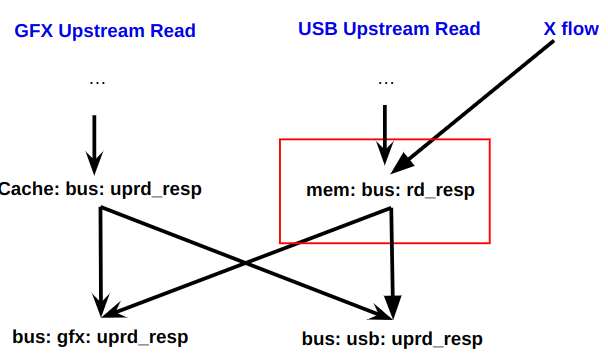

The electronic design automation (EDA) community acknowledges the necessity of specification in system

design and verification. An efficient and reliable set of specifications is the first step toward an

efficient and reliable digital design. The lack of good quality specifications can cause catastrophes in

various safety-critical and mission-critical architectures. Therefore, many endeavors have been carried

out

to determine the correct specifications for reactive systems. Still, none of them obliterated the need

for

further work in this domain. The advancement in ML algorithms specifically in the area of data mining

and large language models (LLM) has opened new research avenues for

specification mining.

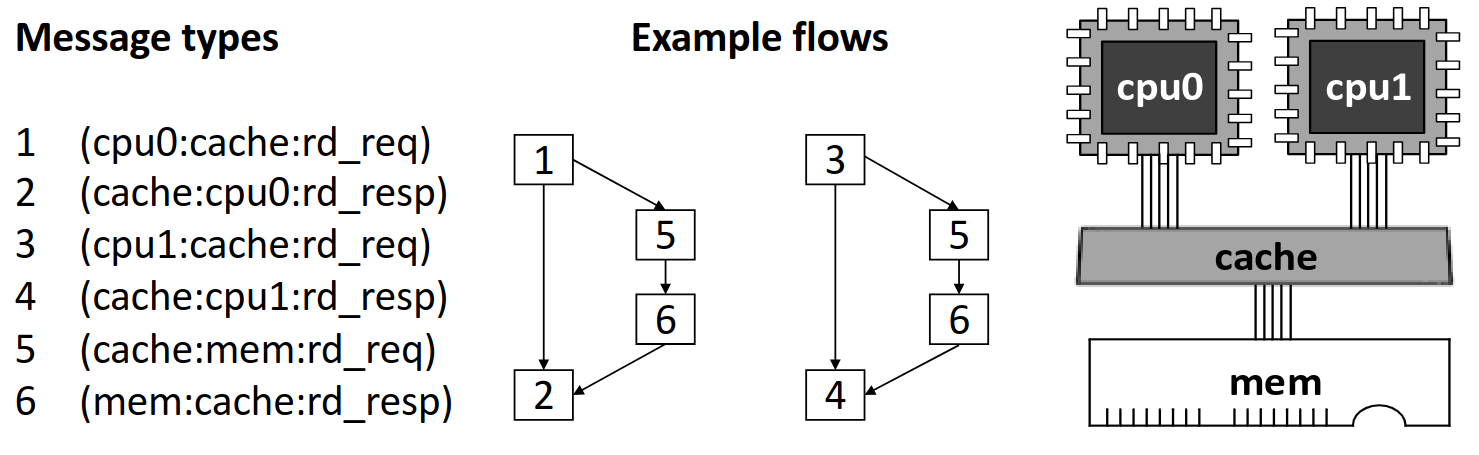

Our contributions in the area of specification mining for SoC post-silicon validation are significant

and ongoing. We initially developed a sequential pattern mining framework to generate specifications

based on execution traces. Recognizing the limitations of this approach, particularly in handling the

exponentially growing search space, we enhanced our methodology by incorporating SAT solver-based trace

modeling. Additionally, we advanced this work through language modeling using BERT, applying large

language models (LLMs) to further improve the accuracy and efficiency of our specifications. This

remains an active area of research within our group. Our findings have been published in prestigious

conferences such as TCAD (transaction), ICCD, ISQED, and MWSCAS.

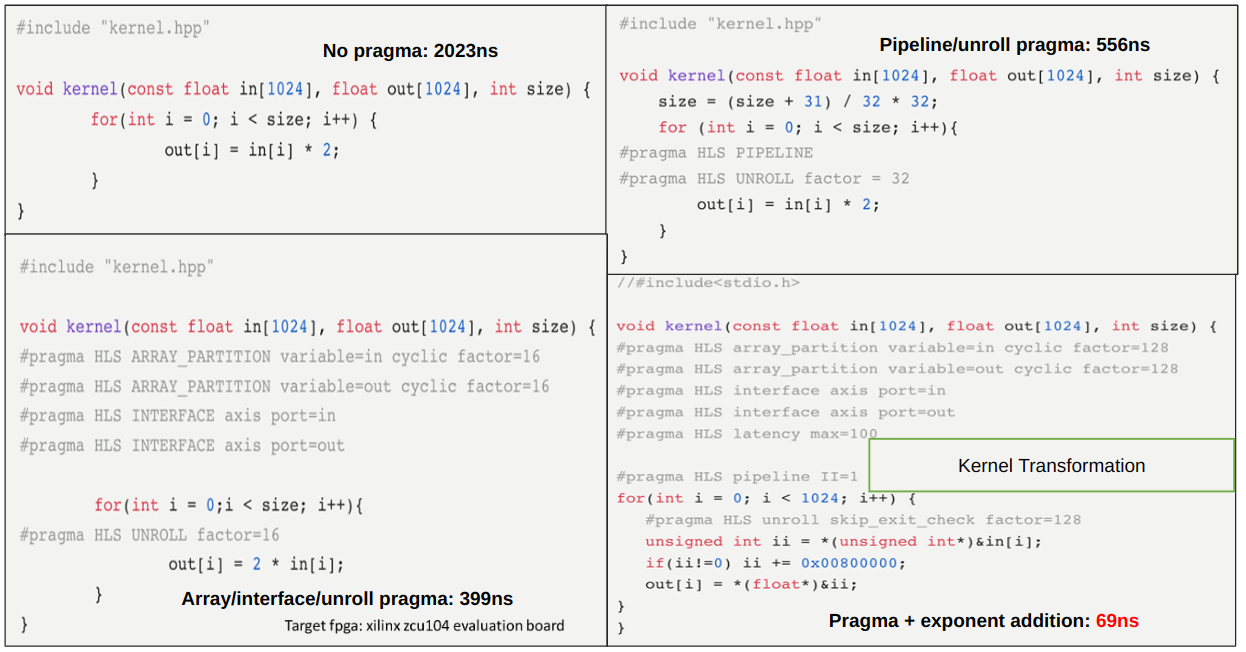

Machine Learning for HLS Acceleration

In the pursuit of knowledge, research is not just a methodical process but a journey of intellectual curiosity, rigor, and perseverance. Every research endeavor is a step towards uncovering truths, challenging assumptions, and contributing to the collective understanding of our world. It is driven by a commitment to uphold the principles of integrity, critical thinking, and continuous learning. As I navigate this journey, I strive to adhere to the guiding principles that have shaped the work of many great scientists before me. I try to follow: The Three Golden Rules for Successful Scientific Research by Dijkstra.

Publications

Please visit my Google Scholar and ResearchGate pages for most recent publication and project updates.

Posters

- Md Rubel Ahmed, Hao Zheng, "Model Synthesis for Communication Traces of System-on-Chip Designs", USF Annual Graduate Student Research Symposium, Mar 2021. (PDF)

- Md Rubel Ahmed, Hao Zheng, "Mining Message Flows from SoC Execution Traces", 57 th Design and Automation Conference (DAC), Jul 2020. (PDF)

- Md Rubel Ahmed, Yuting Cao, Hao Zheng, "Message Flow Mining for SoC Validation for Safe and Secure IoT Edge Node Design", Warren B. Nelms Annual IoT Conference, Dec 2019. (PDF)

- Md Rubel Ahmed, Yuting Cao, Hao Zheng, "Execution Trace Mining for SoC Validation for Safe and Secure IoT Edge Node Design", 2nd IFIP IoT Conference, Oct 2019. (PDF)

- Md Rubel Ahmed, Yuting Cao, Hao Zheng, "Specification Mining For SoC Validation Using Data Mining Techniques", 56 th Design and Automation Conference (DAC), Jun 2019. (PDF)

- Md Rubel Ahmed, Yuting Cao, Hao Zheng, "Specification Mining From Message Flow For SoC Validation", 2019 FICS Research Conference on Cybersecurity, Mar 2019. (PDF)